Rise High-Level Platform

The Deterministic Engine Behind AI-Generated Silicon

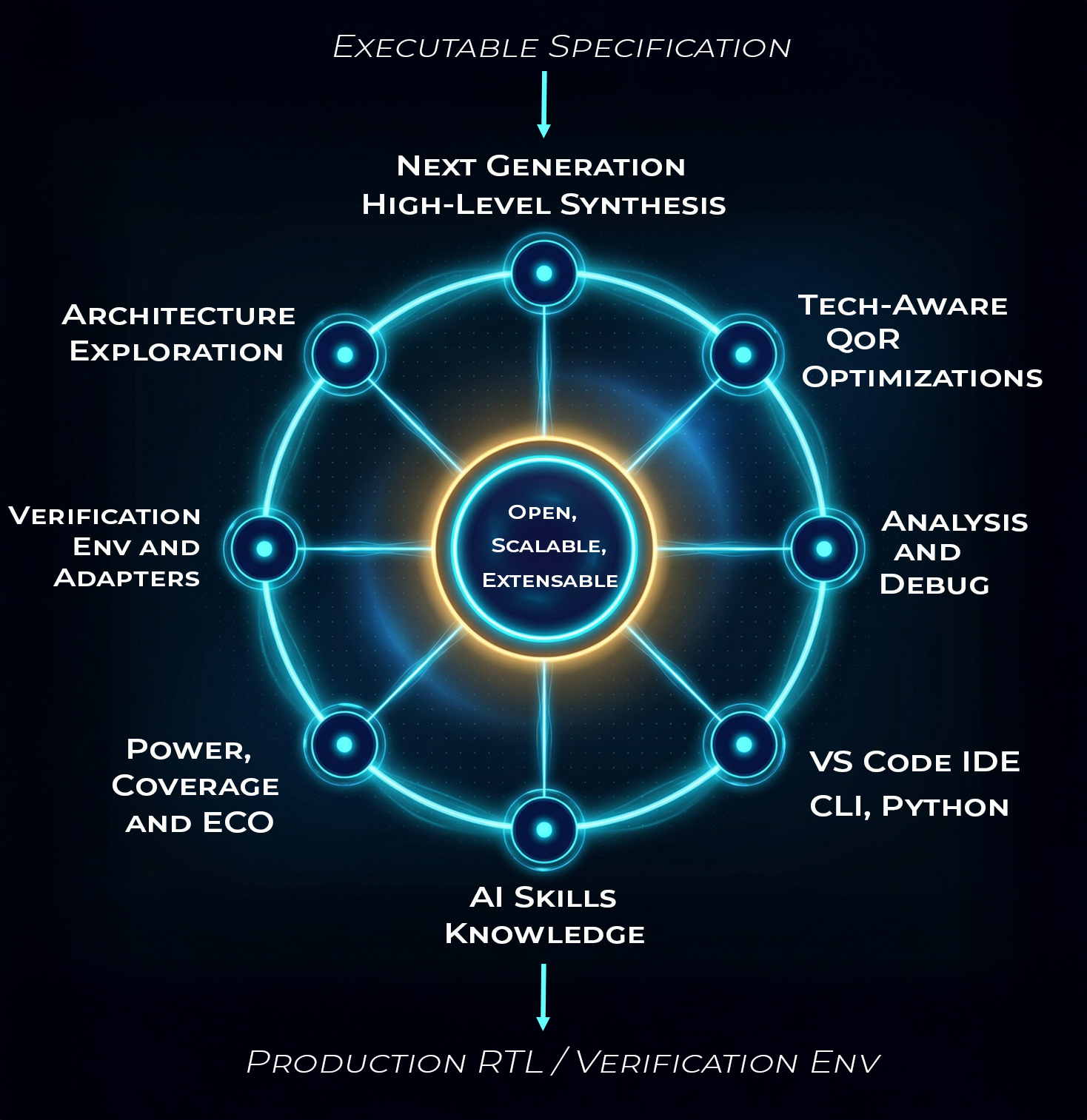

The Rise High-Level Platform is the next-generation synthesis engine that makes AI-generated chip design trustworthy and production-ready. Taking an executable specification, technology-specific synthesis libraries, and pre-built IP as its inputs, it delivers production quality, implementable RTL and a matching verification environment.

Built on an open, scalable, and extensible architecture, the Rise High-Level platform integrates synthesis, verification, and debug and analysis into a single unified environment, delivering results significantly faster than traditional HLS tools. Silicon demands repeatability, traceability, and sign-off confidence and the Rise High-Level Platform is the deterministic foundation that delivers it. Learn more about the features of the Rise High-Level Platform below.

The Executable Specification

The fast and accurate high-level representation of the hardware.

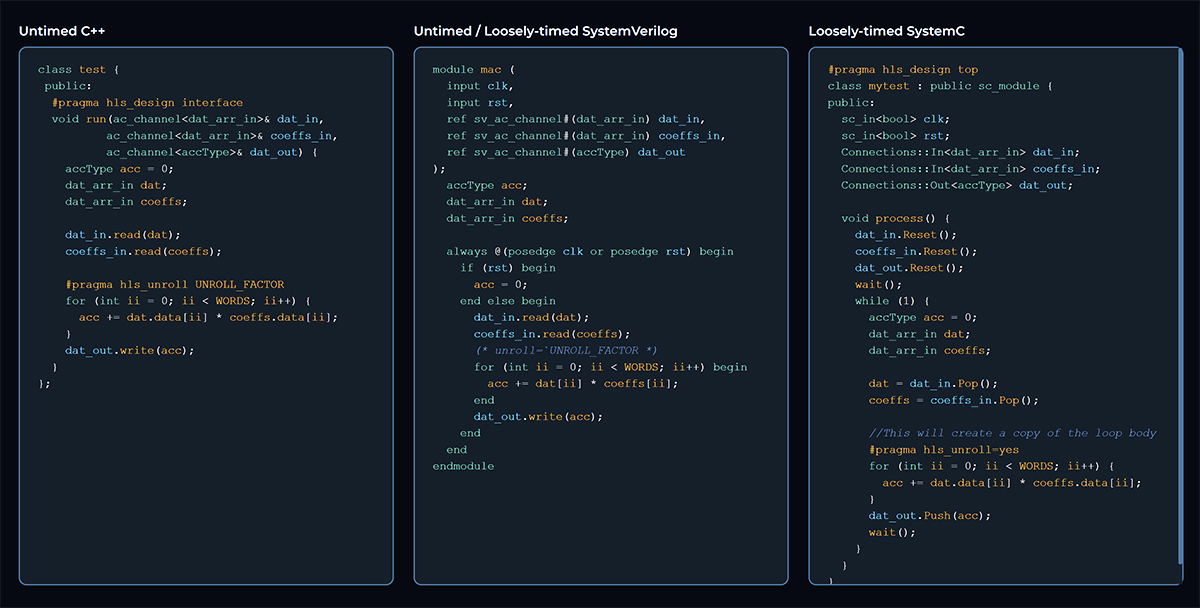

The Rise platform takes an executable specification as its input: a structured, synthesizable representation of hardware functionality and intent. It serves as an accurate high-level model of the hardware for both system-design and high-level design flows, delivering simulation performance 30x–100x faster than RTL. It can be created by hand or by the Rise AI solution, supporting Untimed and Loosely-Timed descriptions across three synthesizable input languages: C++, SystemC, and high-level SystemVerilog, an industry first. This gives design and verification teams the flexibility to work in the language that best fits their expertise, across all design styles from datapath-focused to heavy-control-oriented designs.

All three languages and abstraction levels can be mixed and matched within the same design, enabling teams across different disciplines to collaborate from a common foundation without disrupting existing flows.

Next Generation High-Level Synthesis

High-Level Synthesis That Delivers RTL-Grade Results Faster and More Accurately

The Rise synthesis engine is designed from the ground up to overcome the challenges of existing HLS solutions and close the gap between high-level design intent and production-quality RTL. Rise is 3x to 10x faster than existing HLS tools due to its modern, next-generation architecture. It is also more accurate, integrating RTL synthesis directly into the HLS scheduler to deliver predictable, high QoR results equal to or exceeding hand-coded RTL.

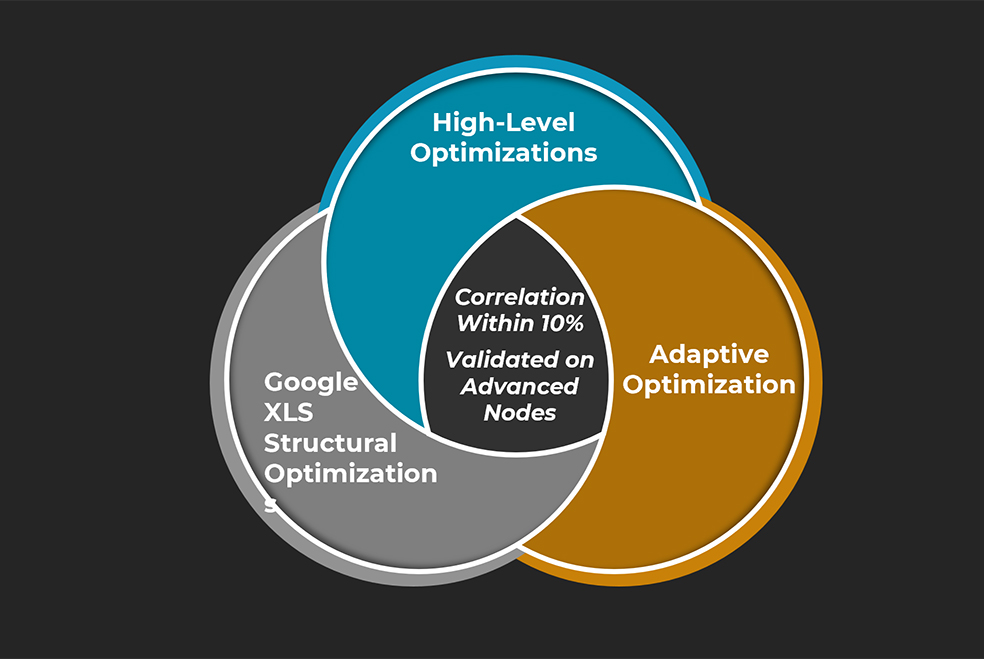

The platform utilizes three unique levels of optimization: high-level optimizations for optimal performance and QoR, adaptive optimization using integrated RTL synthesis, and superior structural optimizations powered by the silicon-proven Google XLS core. The result is RTL that converges quickly and correlates to within 10% of the designers existing production RTL synthesis tools, validated on advanced nodes.

Quality of Results (QoR) Optimizations

Unique Optimizations delivering Superior Results, Faster

When synthesizing a high-level executable specification down to RTL, the output must meet or beat what an experienced RTL designer could achieve by hand. This is the fundamental requirement for any high-level synthesis platform. Rise provides designers with comprehensive tools to achieve this, including full debug visibility and analysis, fast architecture exploration, and AI-guided design assistance. However, at the core of the Rise platform are three unique automated optimizations that are the primary reason Rise consistently delivers superior QoR.

Rise has three levels of unique optimization techniques which deliver the fastest path to high QoR RTL. First, are the high-level optimizations that work at the user source level, preserving user intent while improving debug and performance in ways no other HLS tool can match. Next, Adaptive Optimization integrates RTL synthesis and STA directly into the HLS scheduler, extracting critical paths, updating timing based on real implementation data, and iteratively refining until convergence. Finally, structural optimizations powered by the silicon-proven Google XLS core increase the QoR of the final design. Together, these three optimizations deliver RTL that converges quickly, correlates to within 10% of production RTL synthesis results, and has been validated on advanced nodes.

Analysis, Debug and Compare

Full Visibility From High-Level Specification to RTL

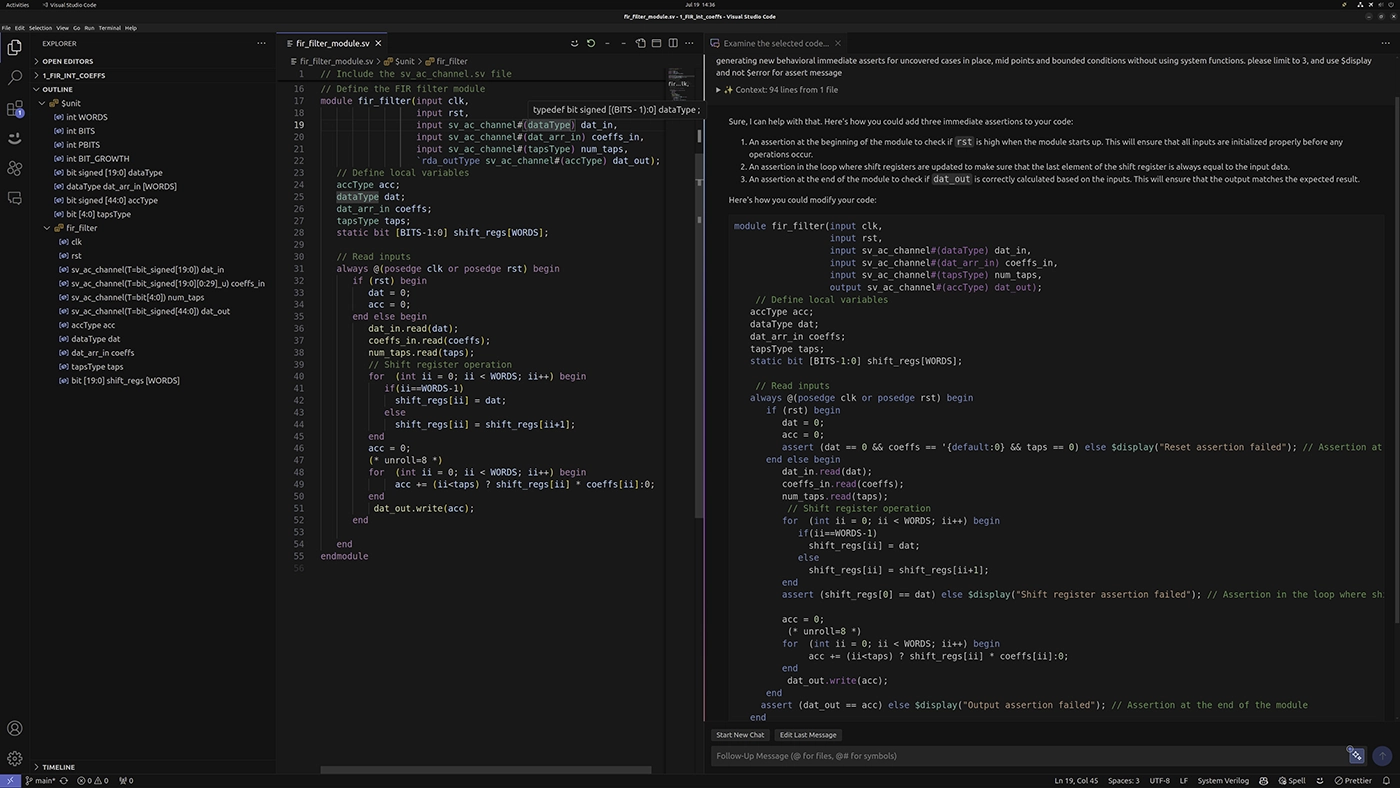

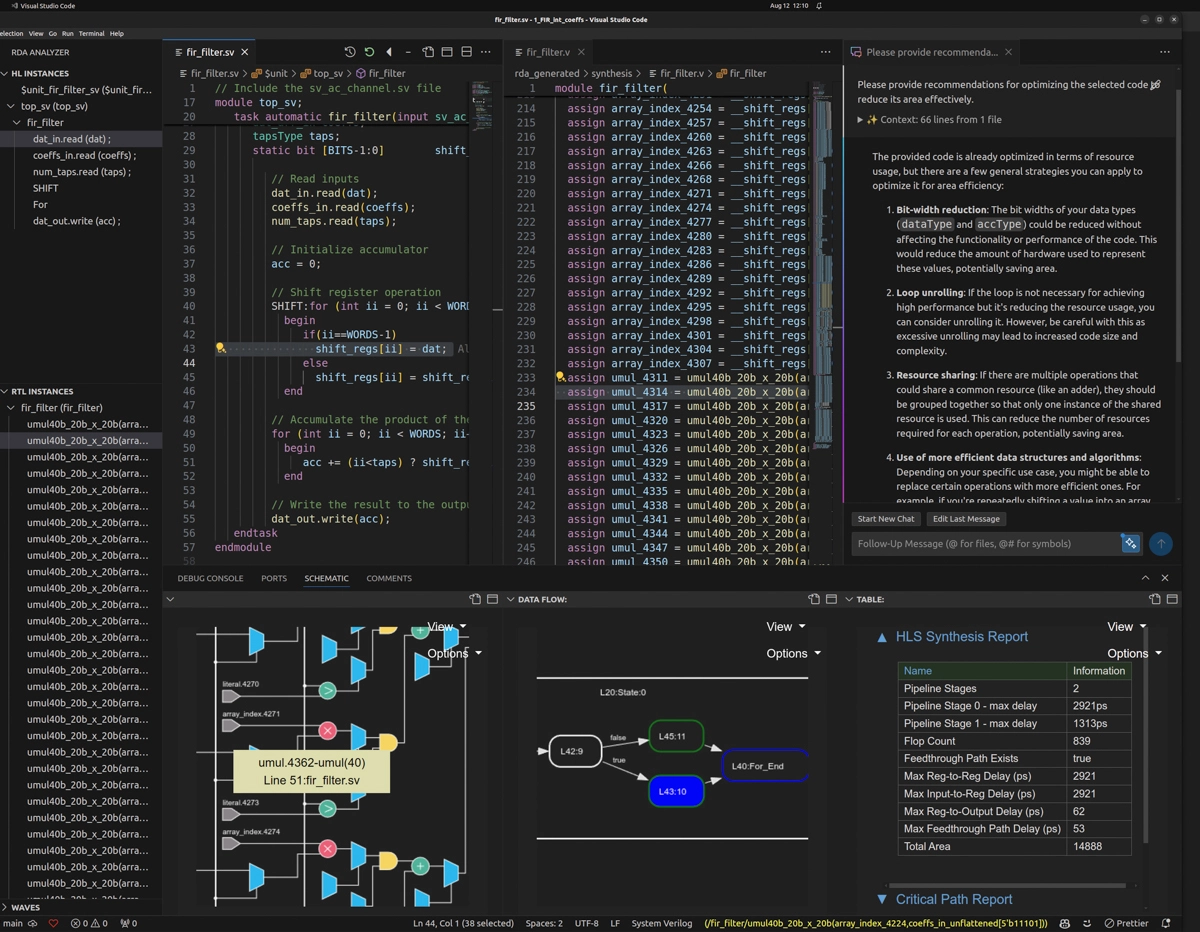

The Rise VS Code IDE provides a unified environment for complete debug and analysis visibility across the full high-level to RTL abstraction range. Working within this environment, designers can trace and correlate waveforms, view source-level analysis, and use dedicated QoR debug windows to quickly understand and fine-tune results.

Beyond basic debug, Rise provides specialized QoR analysis and pre-schedule views that allow designers to optimize design quality early. Interactive reports and graphs such as critical path, control flow graphs, pipeline stage views and other key metrics enable the designer to effectively tune system performance and resolve bottlenecks. Full CLI and Python support further enable scripting, automation, and integration into existing design flows and CI/CD pipelines.

AI Agents and Knowledge

AI Grounded in Hardware Reality

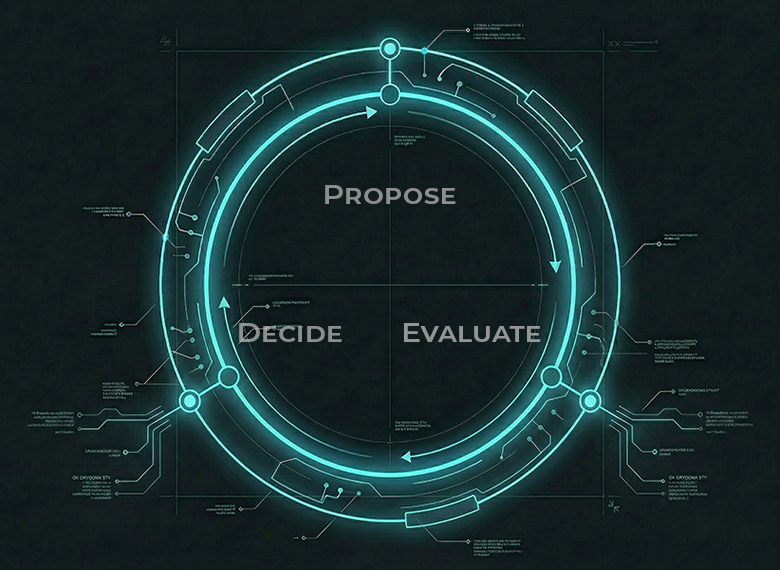

AI Agents with specialized Rise Skills turn system intent into executable specifications through a tool-gated Propose, Evaluate, Decide loop, grounded in a curated knowledge base of hardware IP, coding standards, and domain-specific patterns. The result is deterministic, repeatable outputs that are readable, editable, verifiable, and directly implementable.

Learn more about Rise Agentic AI

Verification Environment and Adapters

Cut Verification Time and Cost by Over 80%

One of the most significant benefits of raising design abstraction is the impact on verification. Users report verification time and cost savings of over 80% driven by 30x to 1,000x faster simulation, 5x to 10x less design code, and catching more than 95% of bugs at the high level where they are faster and easier to find and fix. The result is a true shift-left of verification, enabling teams to start testbench development early and reuse it through RTL.

Adding to this value, Rise automates the generation of verification infrastructure and plug-in adapters that enable mix-and-match of languages and abstraction levels (RTL, SystemC, C++ and SystemVerilog), along with seamless integration into existing SystemVerilog and UVM environments. By operating at the transaction level, the testbench focuses on design intent rather than low-level timing details, making it simpler to write and easier to debug.

Power and Coverage

Early Power and Coverage Insight Without RTL Overhead

Rise provides fast operator-level power analysis estimation at the high level, enabling realistic trend-based analysis for early architectural and scheduling decisions without the overhead of RTL simulation. Power metrics augment verification and validation for full visibility, enabling early identification of worst-case power activity. Detailed power visualization provides instance-based, line-based, and block-level analysis, giving designers the insight they need to make better architectural decisions from day one.

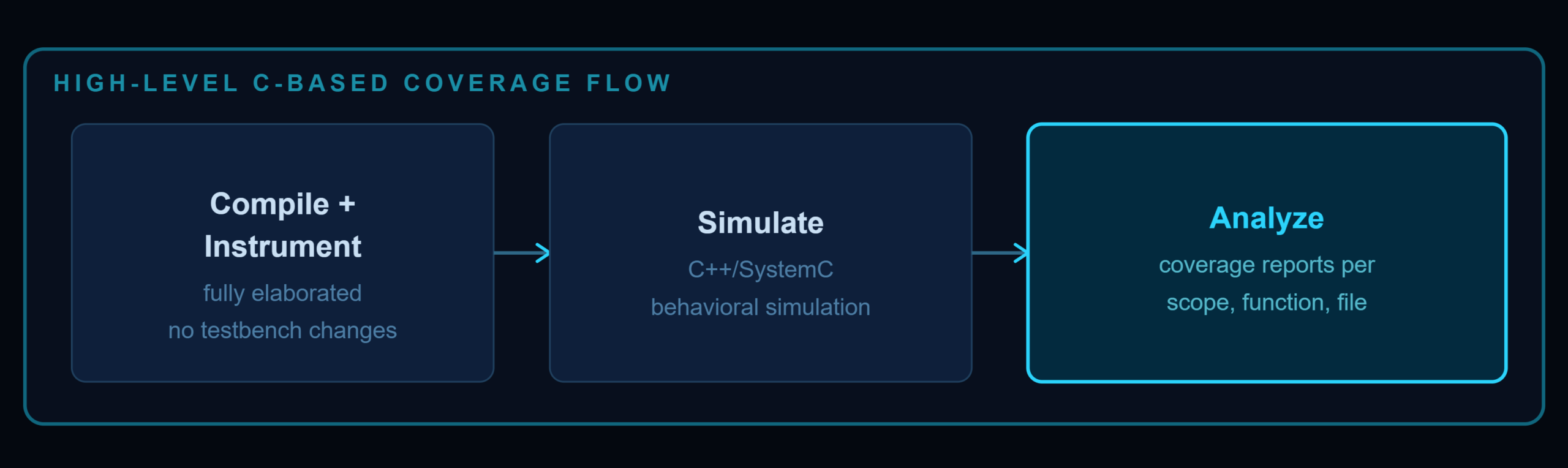

The Rise high-level coverage flow brings the same coverage-driven verification discipline used at RTL to earlier in the design cycle, where simulation is fast and issues are far cheaper to find and fix. When users achieve full coverage at the high level, coverage on the generated RTL follows naturally. If users choose SystemVerilog as their high-level input language, coverage tools are provided by their existing SystemVerilog simulator and coverage provider. If they choose C++ or SystemC, however, standard software-based coverage tools are not adequate for hardware design. Rise addresses this directly, providing comprehensive C++/SystemC structural coverage built with hardware in mind. The flow supports both line and branch coverage, enabling teams to understand exactly which portions of the design have been exercised.

Rise works by instrumenting the user’s high-level code to measure execution coverage during simulation, with no testbench changes required. Because the design is fully elaborated before instrumentation, templated designs are resolved per instance rather than collapsed, and the design hierarchy is preserved throughout. Coverage is collected instance-based across the full function call hierarchy, allowing teams to precisely identify uncovered paths at instance, file, and per-function granularity. The coverage engine is extremely fast and scalable, making it practical for large designs. Fast merge utilities combine coverage results across multiple simulation runs for efficient regression analysis, and results can be analyzed through both textual reports and an interactive UI with flexible sorting and filtering.

High-Level ECO Flow

Incremental Changes with Minimal RTL Disruption

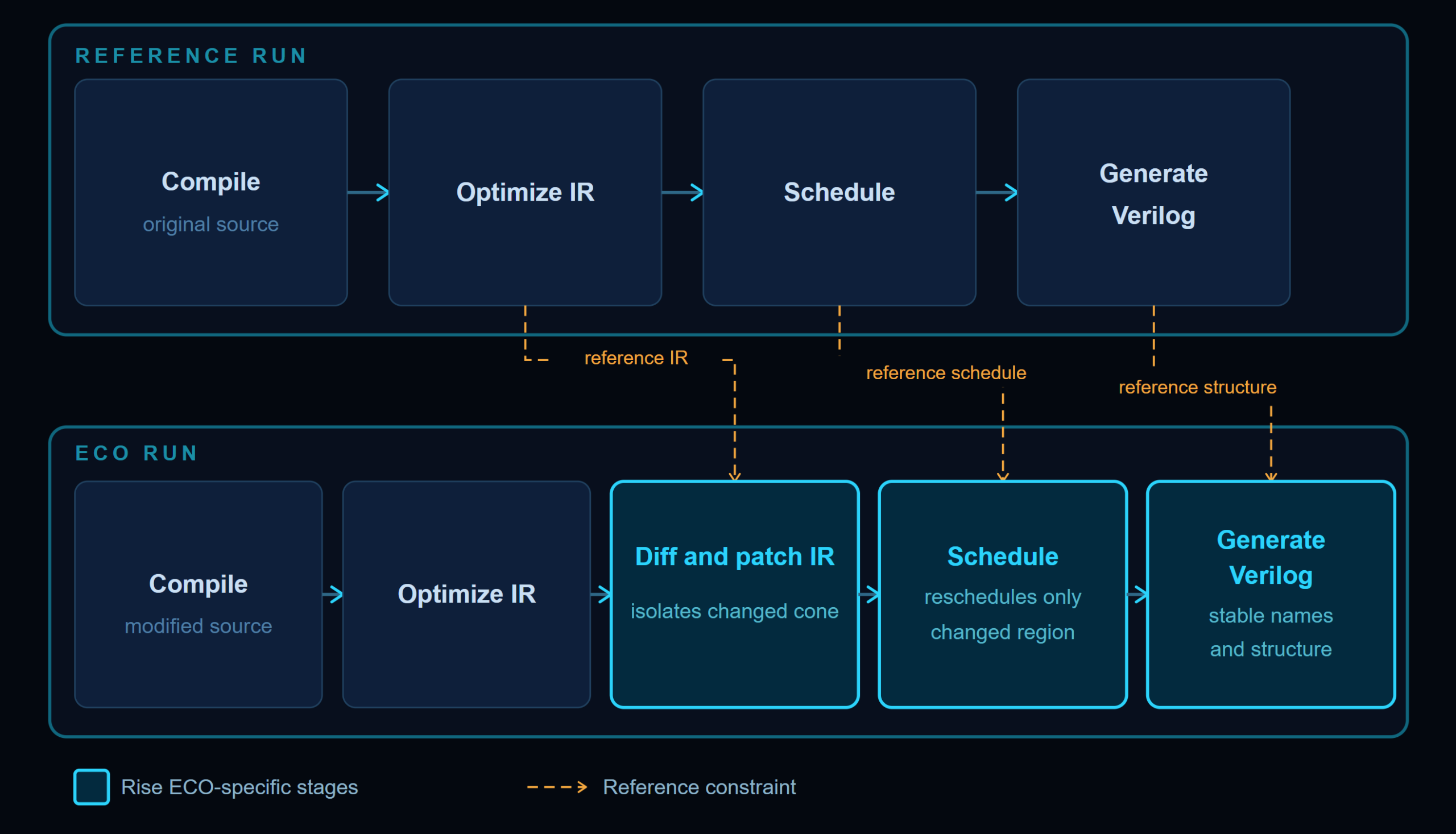

Engineering Change Orders are often unavoidable as requirements shift and silicon fixes arrive late. At the RTL level, designers try to minimize the manual changes that they make and rely on targeted ECO flows and tools. As HLS is generating RTL it must also keep any changes to a minimum. Reacting to late-stage requirements and specification changes is a strength of the HLS methodology because it is possible to completely re-verify the design in a fraction of the time it takes at RTL. Most HLS users say they have never had to implement an ECO in their HLS designs because they were so well verified. When it does occur, however, you need a safe and reliable flow.

The Rise ECO flow solves this directly with a unique approach made possible by the Rise architecture and its multiple open Intermediate Representations (IR). The modified source is compiled through the Rise front-end and its optimized IR is compared against the reference IR using formal equivalence techniques to identify logically equivalent nodes and isolate the affected cone of logic. A minimum-cost patch is applied to the reference IR, so the unchanged design is preserved by construction. Scheduling reschedules only the affected region. The output RTL then preserves the structure and signal naming of the reference, so the resulting difference reflects only the changed logic. Designers can view and analyze exactly what changed between the two versions, with no noise from unrelated structural changes. This RTL can then flow cleanly into their production RTL ECO flow. Incremental source edits yield incremental RTL changes, making ECO in Rise safe, predictable, and minimally disruptive.

Architecture Exploration

Discover Better Architectures Earlier and Easier

Architecture exploration is one of the most powerful and underutilized capabilities in chip design. The ability to generate and evaluate tens to hundreds of design candidates early in the project gives teams the opportunity to discover architectures they would never have found through manual design. The challenge with traditional approaches is that meaningful exploration requires real PPA measurements, and getting those at RTL takes hours per iteration. Rise solves this by operating at the high level where the synthesis loop runs in seconds, delivering PPA measurements that correlate to within 10% of production synthesis tools.

The Rise High-Level Platform supports exploration across all of the key architectural dimensions: loop unrolling to trade off parallelism against area and power, memory architecture including banked memories and circular buffers to optimize internal bandwidth, and interconnect architecture including arbitrated memories and network-on-chip topologies. Changes to any of these parameters are made at the specification level in a fraction of the code required at RTL, and results are available in seconds.

Learn more about AI-Guided Exploration on the Rise Agentic AI page