Delivering Spec to RTL With Confidence

At Rise, we bridge system intent to production-ready RTL with trust built in. We are the industry’s first deterministic AI-native architecture: AI that reasons at the right abstraction level, grounded in hardware knowledge, and validated by real tools. The result is a solution that is practical, scalable, production-ready, and deployable today.

The Semiconductor Industry is at an Inflection Point

and 100x productivity across the entire design flow is needed

The complexity of modern silicon is scaling faster than the tools and processes designed to manage it. New application domains are demanding new architectures, driving costs, complexity, and risk even further. At the same time, hardware must now adapt to evolving software workloads and late changing requirements that turn HW/SW/FW integration into a schedule risk. Today's design flow was not built to scale to meet these demands, and incremental improvements to existing tools and flows are not enough to close the gap.

The industry needs to shift-left the entire design flow and deliver 100x to 1,000x productivity gains over current approaches to keep up. AI is the only scalable path to get there but it must overcome fundamental challenges. Silicon demands correctness, repeatability, and traceability. The question is not whether to use AI it is how to make AI deterministic enough to build silicon with.

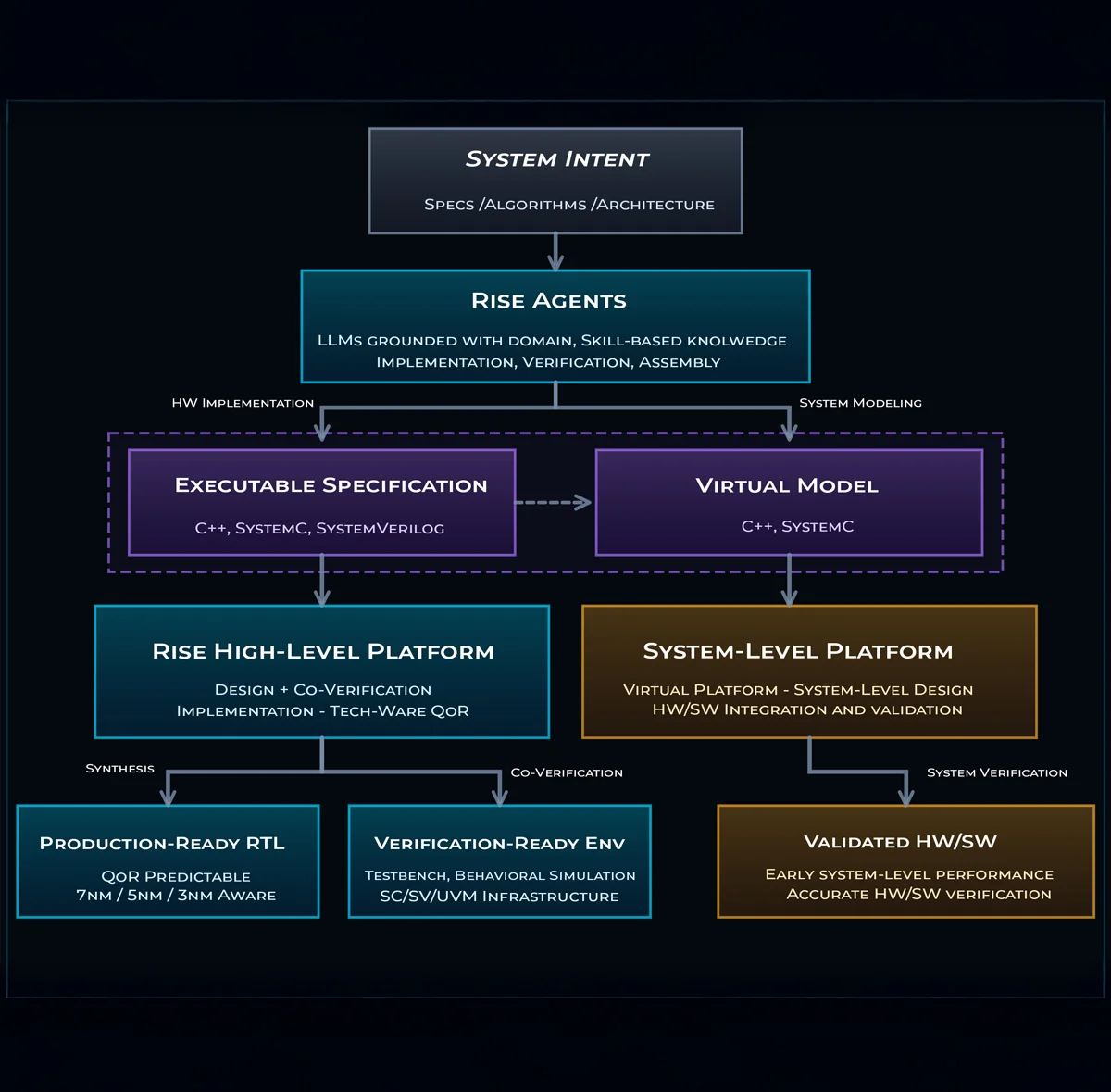

Rise Delivers A New Architecture for Software-Driven Silicon

Rise introduces the industry’s first deterministic AI architecture, an agentic flow that transforms chip design. Starting from a structured specification, the Rise Agentic skills and knowledge generate a high-level executable specification. The agents then use the Rise next-generation High-Level Platform and other EDA tools to validate synthesizability and structural correctness, generate RTL and testbenches, and run simulation to confirm behavioral alignment with the original specification. The entire flow runs in a closed loop, with full visibility for the designer.

Specification

LLM with Rise Skills/Knowledge

Production RTL and Verification Env

This architecture works because every step is grounded in silicon reality. Importantly, Rise is model agnostic, supporting any modern LLM whether frontier foundation models or internal enterprise models. Multiple AI agents with Rise skills reason from domain knowledge to ensure grounded, verifiable transformations. The result is a direct transformation from structured intent to deterministic, technology-aware RTL. This solution is practical, production-ready, and deployable today.

Why Rise Succeeds Where Other AI Solutions Fall Short

Abstraction Advantage and Domain Knowledge

Using AI to generate complex blocks of RTL is fundamentally the wrong abstraction level for large language models. There is limited training data and no good ability to reason about timing, area, or power, and small errors or changes can cause everything to break. Rise has AI operate where it actually excels, at the high level, grounded in a curated hardware knowledge base of coding standards, IP libraries, QoR understanding, and domain-specific hardware patterns. Rise then uses the deterministic Rise High-Level Platform to produce high QoR RTL and a matching verification environment.

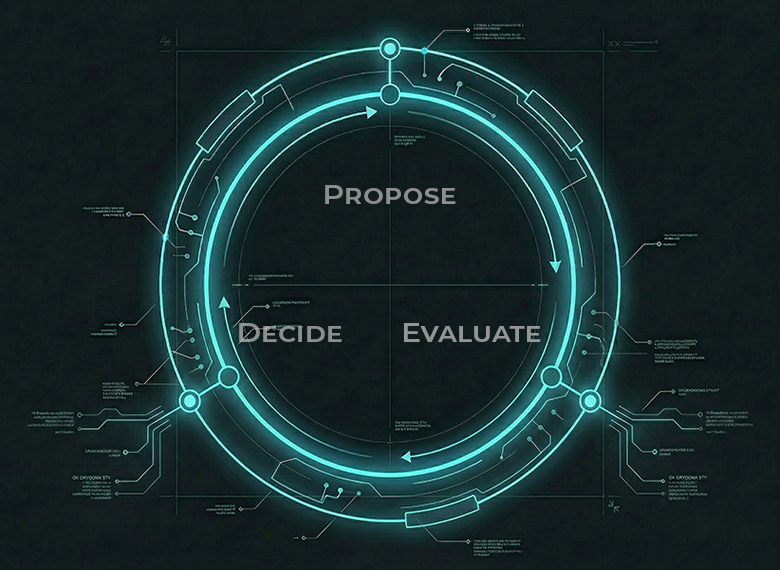

The Closed Loop

Unlike probabilistic approaches, Rise grounds every decision in tool-measured results. The platform runs a continuous Propose, Evaluate, Decide loop: AI proposes high-level candidates, the Rise and other EDA toolchains measures real PPA (Power, Performance and Area), and tool results drive every decision. This is what makes Rise outputs trustworthy and implementable.

Key Benefits

Shift-Left Entire Design Flow

Cut project times from years to months and months to weeks. This is proven on real customer projects. Rise AI and the next-gen Rise High-Level Platform shift-left the entire design cycle and unlock productivity levels not achievable with traditional methods.

Faster Verification and Debug

Achieve 30× to 1,000× faster simulation with proven verification methodologies and comprehensive debugging, enabling teams to find and fix more bugs earlier in the design cycle.

Enable Accurate HW/SW Co-Design

Rise executable specifications provide a single source of truth for RTL accurate hardware functionality with fast simulation, allowing hardware and software teams to work in parallel from day one and eliminate integration and system performance issues.

Explore Architecture and Improve Design Quality

Perform design space exploration at the specification level with closed-loop iterations in seconds, enabling faster PPA optimization and higher-quality, more competitive products.

Easily Handle Late Changing Specifications

Modify or add functionality late in the design cycle and fully re-verify the design at 30x-1,000x over RTL. Retarget to new technology nodes and completely re-time the design in days instead of weeks.

AI-Native and Easy to Adopt

Rise integrates seamlessly into existing design environments, supports SystemVerilog, C++ and SystemC, and leverages an AI-Native flow to generate, optimize, and debug designs automatically while reducing the learning curve.

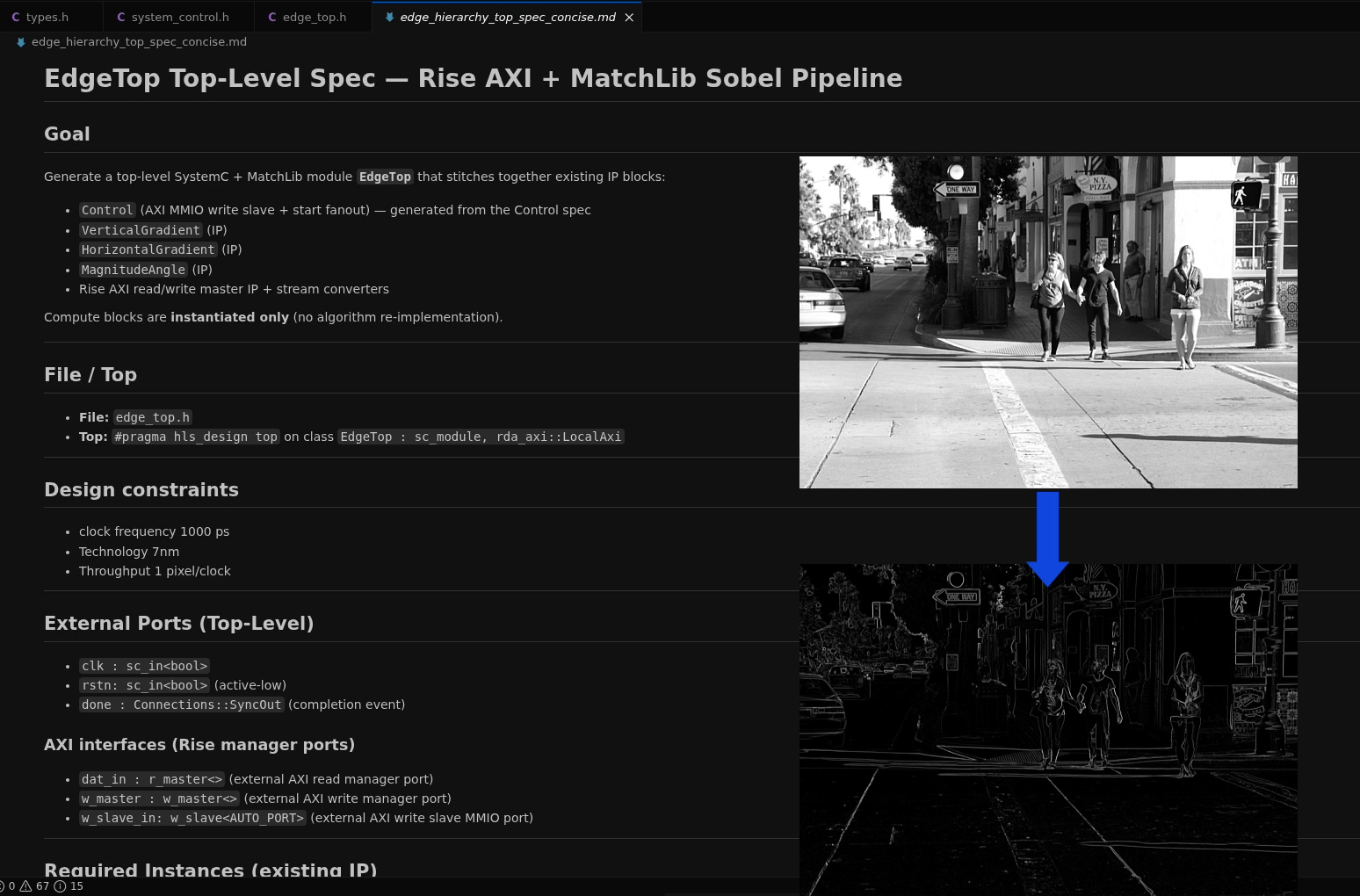

See Rise in AI Solution Action

Watch how Rise transforms a structured design specification into synthesized, validated RTL with full visibility at every step. This 5-minute demonstration steps through the flow showing the tool, AI and user interactions to take a Sobel edge detection algorithm into an AXI-based accelerator in RTL that is verfied functionally correct and meets design specification of 1 pixel per clock.