Rise Overview

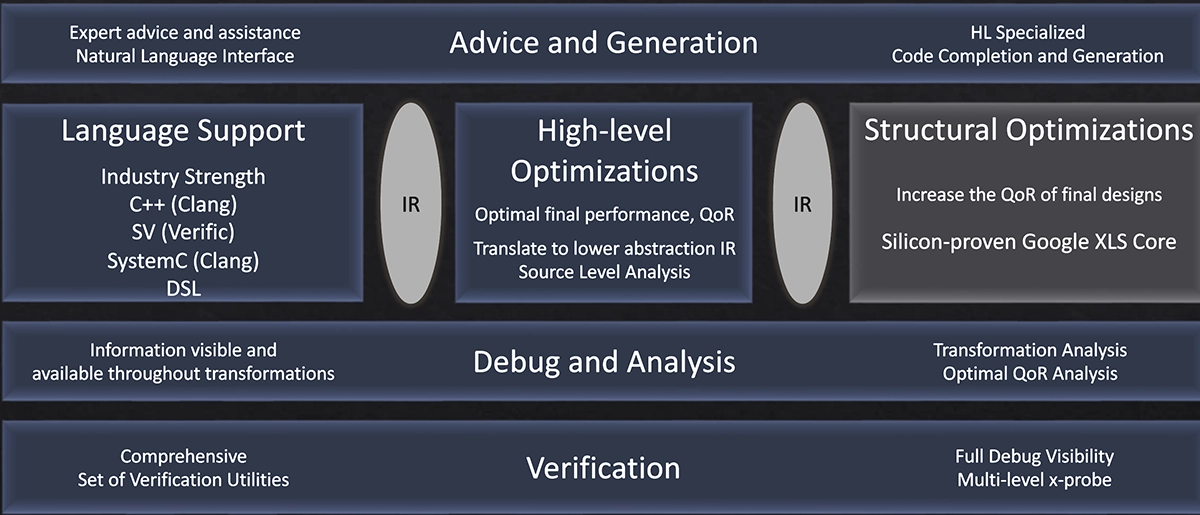

Discover the groundbreaking Rise suite of tools, uniquely architected to accelerate next-generation hardware design projects with adoption at scale and innovation at scale. From industry-first SystemVerilog support to the power of dedicated AI throughout, Rise revolutionizes all aspects of hardware design, verification, debug and analysis.

Rise Language Support

Rise’s unique architecture enables it to be language agnostic. It is the industry’s first multi-language, multi-abstraction High-Level Synthesis, Verification, Debug, and Analysis suite of tools supporting SystemVerilog , C++ and SystemC. This allows Rise to leverage existing high-level IP available in C++ and SystemC while introducing new capabilities, flexibility and broader adoption through SystemVerilog.

By incorporating high-level SystemVerilog (SV), we significantly lower the barrier to adoption for both RTL and verification engineers and expand the range of design styles that can be supported. SV is a natural language for expressing a designer’s intent, allowing them to work within a familiar language and environment. Additionally, with SV, designers can choose between untimed or loosely-timed high-level coding styles, offering complete flexibility to increase abstraction while maintaining control.

Rise Synthesis

Our tool seamlessly transforms high-level language descriptions into synthesizable RTL, ready for implementation. Users can begin with a high-level design, describing functionality and algorithms using SystemVerilog, C++, or SystemC. This high-level description is then synthesized into RTL, which is optimized to meet the design specifications.

Rise synthesis delivers predictable Quality of Results (QoR) quickly, without requiring users to be experts in high-level design tools. We employ a four-step approach to consistently achieve these results.

Four Steps to Achieve Synthesis QoR

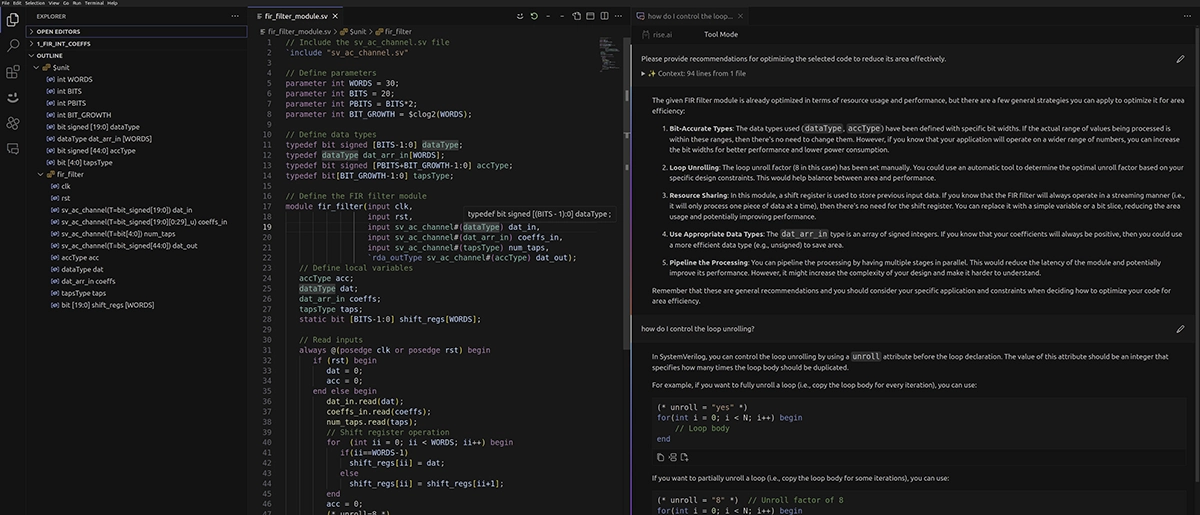

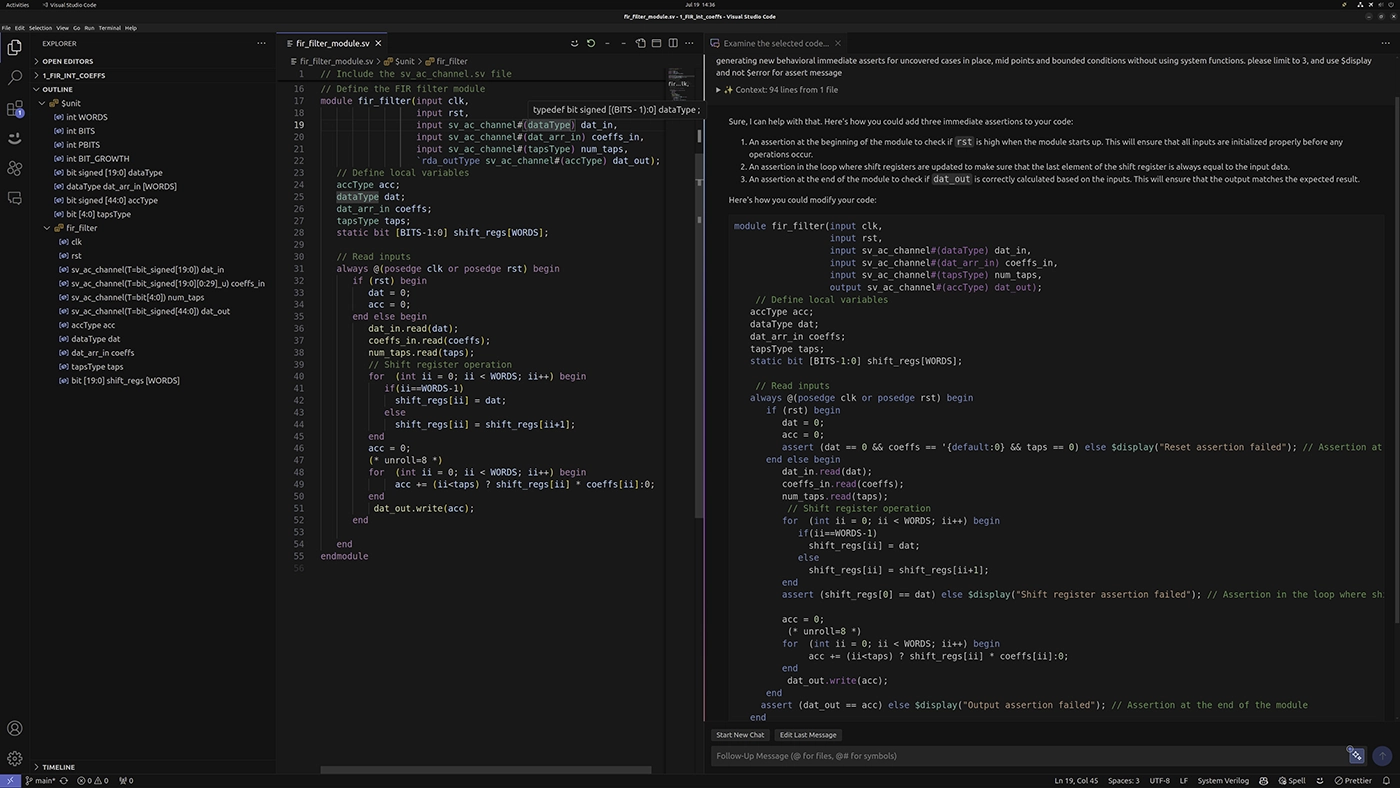

Rise.ai Advisor

Rise has developed the industry’s first generative AI Advisor specifically tailored for high-level design, seamlessly integrated into the tool chain and design flow. This AI Advisor utilizes uses natural language input, allowing users to have a tool and high-level expert at their side. It assists with various tasks including the creation of designs in SystemVerilog, SystemC and C++ and test benches in both C++ and UVM, and provides guidance on rewriting code for optimal Quality of Results (QoR) – just to name a few.

Two Levels of Synthesis Optimization

Rise employs a unique two-level optimization process during synthesis. The first level focuses on high-level optimizations, where we optimize at the user source level, preserving design intent and enabling more tailored optimizations for each source language. The second level is structural optimization, which handles tasks such as technology mapping, pipelining, and more. This dual approach results in synthesis run times that are an order of magnitude faster, with outcomes that are not only more predictable but also easier for users to understand and debug.

Design Space Exploration

Because Rise synthesis is so fast, it can be used to explore all possible combinations to find optimal solutions and/or architectures. This enables designers to find solutions that they did not have time to consider and be confident that they are not leaving any QoR on the table.

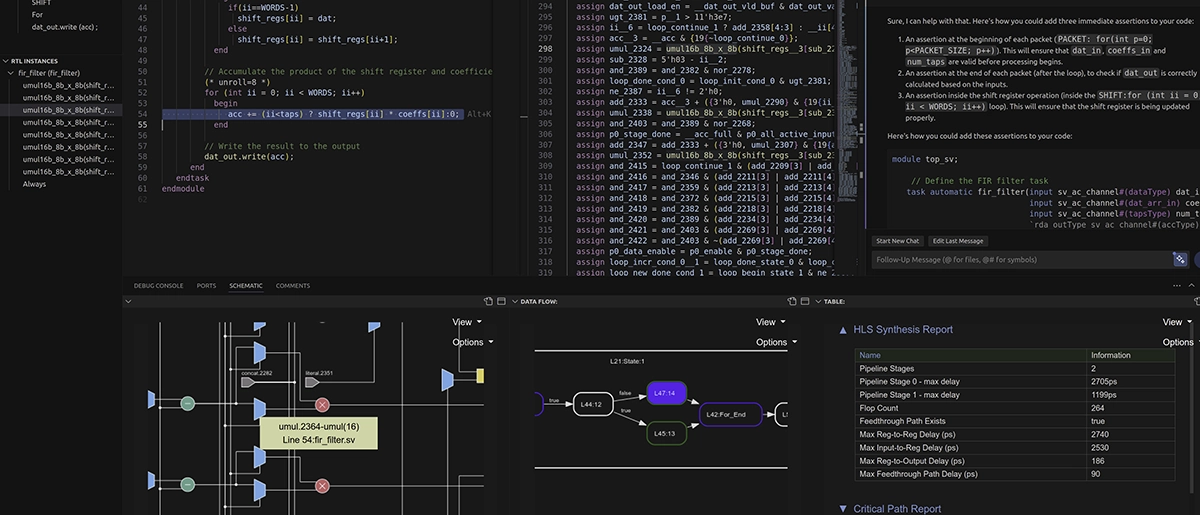

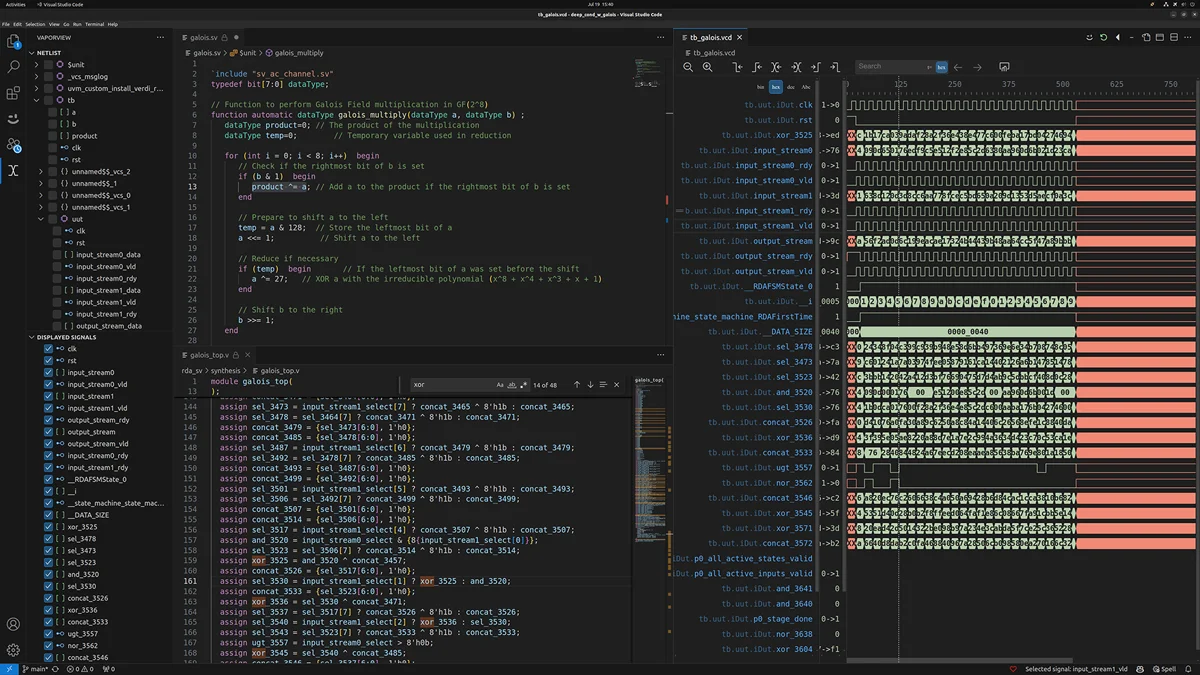

Debug and Analysis

Rise’s debug and analysis tools provide full visibility at every stage of the transformation from high-level source code to RTL, presenting this information to the user in easily queryable, filterable, and fully cross-probeable views. Our dedicated QoR analysis views allow designers to quickly identify and resolve issues directly within their high-level source code.

Rise Verification

One of the most significant benefits of raising the design abstraction level is the dramatic improvement in verification simulation speeds, ranging from 100x to 1,000x faster. However achieving verification confidence using higher abstraction levels can be challenging. Rise addresses this by making high-level verification a central component of our solution, delivering orders of magnitude overall faster verification compared to traditional methods.

We provide predictable high-level verification from block-to-system, built on a native SystemVerilog foundation and supporting multi-threaded C++. Our approach uniquely supports the verification of multiple design styles at the high-level, enabling the early detection of even the most challenging bugs and system performance issues.

Rise also offers true mix-and-match capability across both language and abstraction, allowing users to seamlessly swap between high-level and RTL representations while maintaining the same testbench and environment. Our verification solution includes automatic channel capture for waveforms, automatic high-level to RTL comparisons, and a comprehensive set of utilities and examples for sub-system assembly and verification testbenches. Rise verification provides unparalleled ease, flexibility, and confidence from high-level design through RTL, and from block to system.

Rise Analyzer

Built on the modern Microsoft VS Code Platform, our high-level debug and analysis solution offers full visibility for both synthesis and verification, with complete correlation and traceability from high-level code to RTL across source files, schematics and waveforms. Rise Analyzer includes dedicated QoR debugging features, with detailed interactive reports that allow for quick understanding and fine-tuning of synthesis results. Additionally, built-in and customizable waveform dumping supports high-level block and system-level verification and debugging.

The AI-powered high-level Advisor is seamlessly integrated, enabling effortless interaction between the tool, the design and the Advisor for the ultimate debugging guidance. This ensures comprehensive analysis and debugging capabilities throughout the entire design and verification process.

Rise.ai Advisor

Quickly create high-level design and verification code sections using advanced AI capabilities, integrating best practices and effective refactoring to achieve superior design quality and results. With expert guidance improve performance and reduce power consumption.

The success of scaling AI relies heavily on the quality and relevance of the data used. Rise.ai’s high-level data abstraction, combined with domain-specific knowledge bases, simplifies processes, making them more scalable and manageable. This approach provides users with specialized, expert advice and accurate information quickly, significantly reducing the time and effort required compared to traditional EDA flows.

With Rise, engineers can design complex semiconductor hardware as intuitively as having a conversation, with an expert by their side.