Rise Design Automation

Watch the full interview with Badru Agarwala, co-founder and CEO, discussing what Rise is all about

Our Mission

Our mission at Rise Design Automation is to raise the level of abstraction of design and verification beyond RTL and have it adopted at scale across the industry in order to transform how designs will be done for years to come. So, Adoption at Scale with Innovation at Scale.

The Challenge

Driven by multiple high growth markets such as next-generation AI applications, 5G/communications, and the proliferation of smart devices, the semiconductor market is experiencing unprecedented growth – predicting to surpass $1 Trillion by 2030. However, semiconductor hardware design abstractions and methodologies have not significantly changed in over 20+ years. Coupled with the end of traditional compute acceleration and the lack of engineering resources, the industry is reaching an inflection point where only dramatic improvements in productivity will be able to meet demand and companies maintain a competitive edge. It is predicted by 2030, the U.S. semiconductor sector alone could face a shortage of almost 40,000 hardware engineers.

Adoption at Scale

There have been multiple efforts to raise the level of abstraction of hardware design above (Register Transfer Level) RTL, but none have achieved widespread success or adoption. There are three major classes of challenges that must be addressed to achieve adoption at scale. To date, only Rise has effectively addressed all three of these challenges.

Language barrier

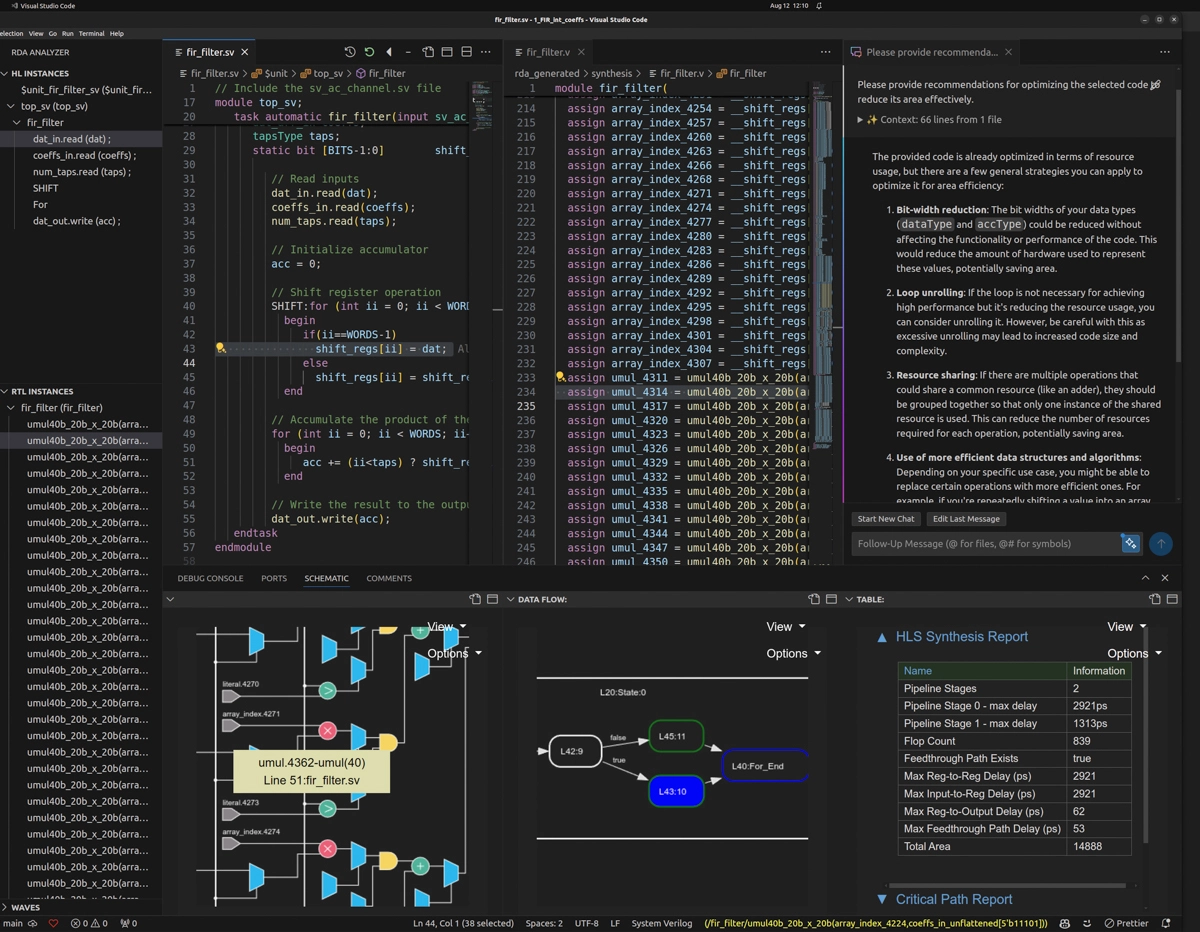

Delivering the industry’s first multi-language, multi-abstraction SystemVerilog, C++, and SystemC High-Level Synthesis, Verification, Debug and Analysis Suite of tools…

Predictable and Superior Synthesis Quality of Results(QoR)

Rise leverages four unique technologies, including the industry’s first high-level Generative AI, to deliver fast and predictable Quality of Results (QoR) without requiring users to be high-level design experts.

Verification confidence

One of the greatest benefits of raising the design abstraction level is the substantial improvement in simulation speed and verification productivity. Rise uniquely enhances verification confidence by employing trusted SystemVerilog for verification, while also enabling designers to seamlessly integrate it with various design languages and abstraction levels.

Innovation at Scale

To address the significant challenges of raising the abstraction level, Rise has developed a modern, modular, and scalable architecture from the ground up. In this new architecture, multi-language support, Quality of Results (QoR), verification, generative AI, and debugging are all treated as first-class citizens.

We have built our environment on a strong foundation by leveraging industry-leading tools: Clang for C++, Verific for SystemVerilog, Microsoft Visual Studio for our IDE and debugging, Google XLS for our Intermediate Representation (IR) and structural optimization, and Cody for our AI front-end and a multi-LLM approach. Rise is not only driving its own rapid innovation but also benefiting from the continuous advancements of these modern packages.

With this architecture, we can innovate at a much faster pace and seamlessly integrate new languages and tools into the Rise environment. This has led to consistently faster and easier bring-up of designs from across the open-source community.

Key Benefits

Dramatically Boost Productivity:

Achieve faster and more efficient implementations with less effort by raising the design abstraction level above RTL.

Improved Design Quality and Products:

With superior Quality of Results (QoR) and faster synthesis, PPA optimized design solutions can be found and validated

Faster Derivative Products and More Competitive Products:

Easily modify and add new functionality late in the design cycle, with the ability to fully re-verify and/or retarget to new technology nodes in days rather than weeks.

Easier Adoption:

Full support for SystemVerilog, C++ and SystemC for multi-level mixed abstractions enable easier adoption into existing design environments.

Faster Verification and Debug:

Built-in and proven verification methodologies and comprehensive debug enable finding more bugs faster and earlier

Leverage AI Everywhere:

Quickly create high-level design and verification code sections using advanced AI capabilities, integrate best practices and effective refactoring for superior design quality and results, improve performance and reduce power consumption with expert guidance.